Font AMD Ryzen: fons de pantalla AMD

AMD té molts productes apassionants en el seu oleoducte i les expectatives són molt elevades per al llançament de la sèrie Ryzen 3000. El primer llançament de Ryzen el 2017 va ajudar els consumidors a obtenir una segona opció en un mercat dominat per Intel. El llançament de Ryzen 2000 l’any passat va millorar molt la fórmula de llançament, oferint velocitats de rellotge més altes i més nuclis. Es preveu que la sèrie 3000 de Ryzen faci més del mateix, oferint encara més nuclis (segons fuites) i velocitats de rellotge més altes.

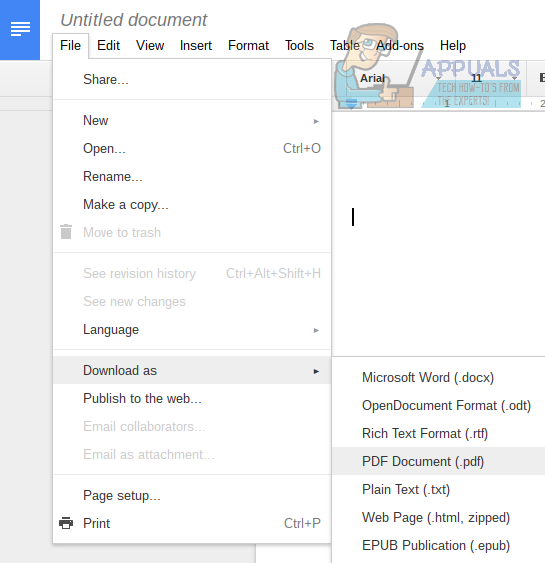

Zen2 ÉS 16 Core

Rellotge base 3,3 Ghz ฺ

Rellotge Boost de 4,2 Ghz

MB X570

Aquest nom de CPU no es pot descodificar per gràfic de descodificació

PS (la captura de pantalla es pot penjar més endavant).

- APISAK (@TUM_APISAK) 9 de maig de 2019

Fins ara, les filtracions han indicat processadors 16C / 32T a la gamma Ryzen, cosa que només es veia als xips Threadripper. Aquest tuit anterior confirma el mateix. Indica una mostra d'enginyeria Zen 2 amb 16 nuclis. Funciona amb una placa x570 amb un rellotge base de 3,3 GHz i un rellotge d’augment de 4,2 GHz. Els rellotges es troben a la part inferior, probablement perquè es tracta d’una mostra d’enginyeria. El Ryzen 2700x pot fer 4,2 GHz amb un overclock decent, de manera que els xips similars de la sèrie 3000 haurien de superar.

Algunes mostres d'Enginyeria de la primera generació Ryzen tenien una base de 2,7 GHz / 3,2 GHz turbo, que al llançament tenia una base de 3,6 GHz / 4 GHz. Podem esperar millores en la mateixa línia en el llançament. El xip de mostra aquí és probablement el Ryzen 3800, que segons les filtracions se suposa que té 16 nuclis.

Zen 2 Architecture

Zen 2 formarà part del procés de 7 nm de TSMC, que inclourà les fitxes Ryzen i Epyc Rome d’aquest any. Els rumors suggereixen un augment de l'IPC en el rang del 10 i el 20 per cent.

El unitat de coma flotant va patir importants modificacions al Zen 2. In Zen , AVX2 Es van donar suport a tipus de dades de coma flotant de vector de precisió única i doble de 256 bits mitjançant l’ús de dues microoperatives de 128 bits per instrucció. De la mateixa manera, les operacions de càrrega i emmagatzematge en punt flotant tenien una amplada de 128 bits. A Zen 2, el ruta de dades i la unitats d'execució es van ampliar a 256 bits, duplicant el rendiment vectorial del nucli.

Amb dos de 256 bits FMA , Zen 2 és capaç de tenir-ne 16 FLOPs / cicle.

- Wikichip

Això augmentarà directament el rendiment pur de la CPU. Zen 2 també utilitza Infinity Fabric 2, que oferirà una taxa de transferència més alta per enllaç, també una comunicació més ràpida entre nuclis, ajudant també a mantenir la latència de la memòria uniformement baixa. El consum d'energia per a un rendiment similar ha de ser menor a causa del procés més petit.

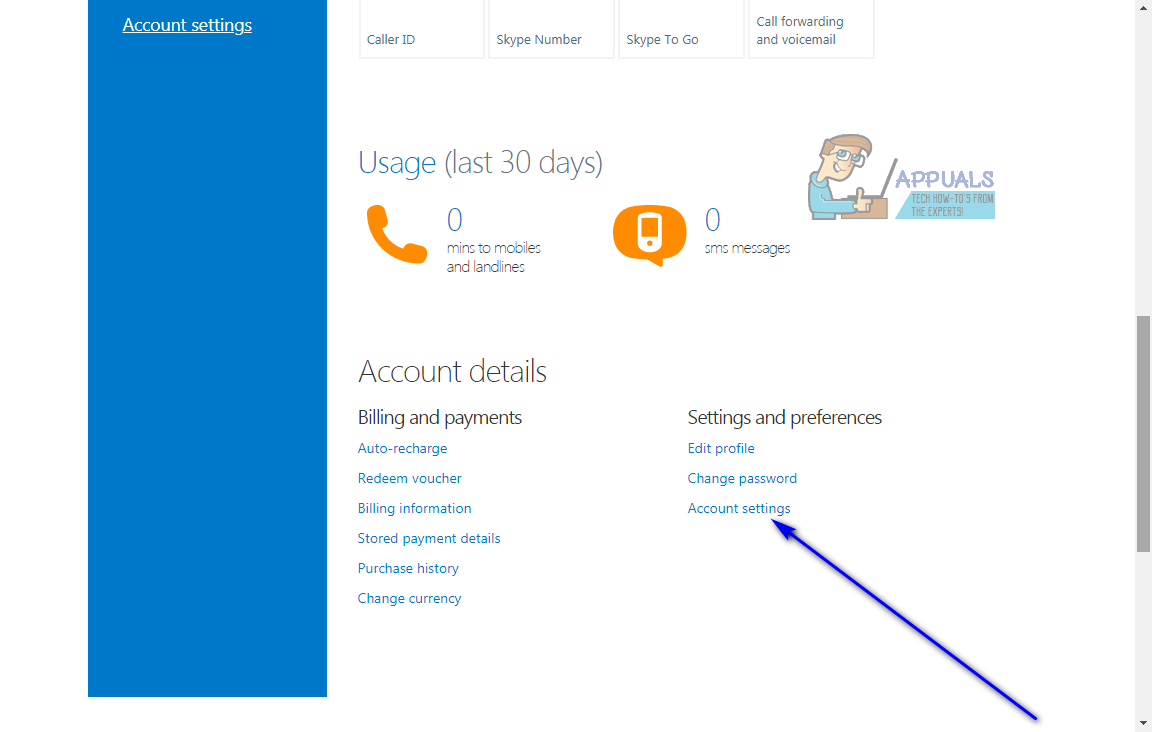

Plaques base X570

Els xips de la sèrie 3000 de Ryzen seran compatibles amb la versió anterior, ja que faran servir el mateix sòcol AM4, sempre que es compleixin els requisits d’alimentació. Les plaques x470 amb xips de la sèrie Ryzen 2000 aporten suport a Precision Boost Overdrive i XFR 2.0. Els xips de la sèrie Ryzen 3000 amb plaques x570 proporcionaran suport per a PCIe 4.0.

PCle 4.0 també hauria de funcionar en algunes taules x470 i x370, TomsHardware en un dels seus articles afirma ' Hem parlat amb representants d'AMD, que han confirmat que les plaques base AM4 de les sèries 300 i 400 poden admetre PCIe 4.0. AMD no bloquejarà la funció de sortida, en canvi , dependrà dels proveïdors de plaques base validar i qualificar l’estàndard més ràpid de les seves plaques base cas per cas. Els proveïdors de plaques base que admetin la funció ho permetran mitjançant actualitzacions del BIOS, però aquestes actualitzacions vindran a criteri del proveïdor. Com s'esmenta a continuació, el suport es podria limitar a les ranures a bord , dissenys de commutació i mux. '

AMD llançarà oficialment la sèrie Ryzen 3000 a Computex aquest any, que queda a poques setmanes.

Etiquetes amd Ryzen

![[Actualització: guanyen els proveïdors] Microsoft acabaria amb els drets d’ús intern dels seus socis, cosa que no significava l’ús gratuït dels productes i serveis de MS](https://jf-balio.pt/img/news/05/microsoft-was-end-internal-use-rights.jpg)